# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

### **General Description**

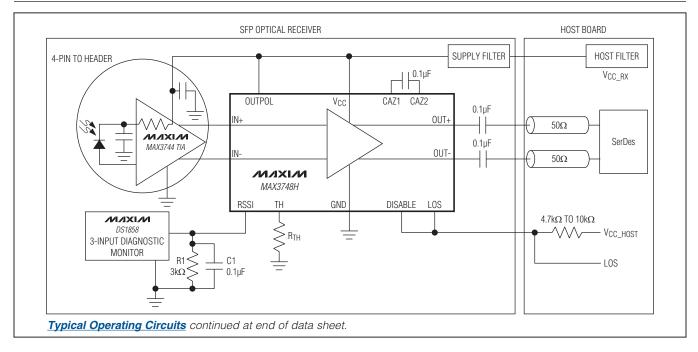

The MAX3748H multirate limiting amplifier functions as a data quantizer for SONET, Fibre Channel, and Gigabit Ethernet optical receivers. The amplifier accepts a wide range of input voltages and provides constant-level current-mode logic (CML) output voltages with controlled edge speeds.

A received-signal-strength indicator (RSSI) is available when the MAX3748H is combined with the MAX3744 SFP transimpedance amplifier (TIA). A receiver consisting of the MAX3744 and the MAX3748H can provide up to 19dB RSSI dynamic range. Additional features include a programmable loss-of-signal (LOS) detect, an optional disable function (DISABLE), and an output signal polarity reversal (OUTPOL). Output disable can be used to implement squelch.

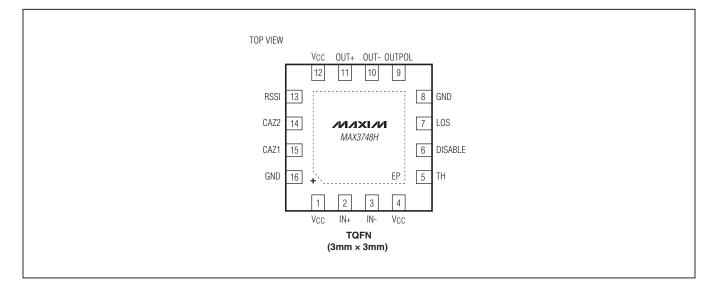

The combination of the MAX3748H and the MAX3744 allows for the implementation of all the small-form-factor SFF-8472 digital diagnostic specifications using a standard 4-pin TO-46 header. The MAX3748H is packaged in a 3mm x 3mm, 16-pin thin QFN package with an exposed pad.

## Features

- SFP Reference Design Available

- 16-Pin TQFN Package with 3mm x 3mm Footprint

- Single 3.3V Supply Voltage

- ♦ 86ps Rise and Fall Time

- Loss of Signal with Programmable Threshold

- ♦ RSSI Interface (with MAX3744 TIA)

- Output Disable

- Polarity Select

- ♦ 8.7psp-p Deterministic Jitter (4.25Gbps)

### **Applications**

Gigabit Ethernet SFF/SFP Transceiver Modules Fibre Channel SFF/SFP Transceiver Modules Multirate OC-3 to OC-48-FEC SFF/SFP Transceiver Modules

Ordering Information appears at end of data sheet.

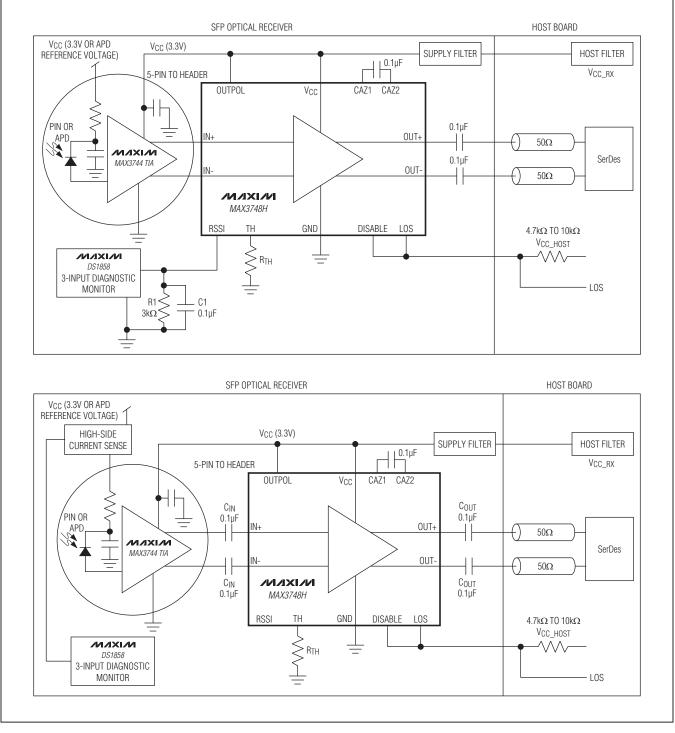

## **Typical Operating Circuits**

For related parts and recommended products to use with this part, refer to: www.maxim-ic.com/MAX3748H.related

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

### **ABSOLUTE MAXIMUM RATINGS**

| Power-Supply Voltage Range (V <sub>CC</sub> )0.5V to +6.0V      |

|-----------------------------------------------------------------|

| Voltage Range at IN+, IN $(V_{CC} - 2.4V)$ to $(V_{CC} + 0.5V)$ |

| Voltage Range at DISABLE, OUTPOL,                               |

| RSSI, CAZ1, CAZ2, LOS, TH0.5V to (V <sub>CC</sub> + 0.5V)       |

| Current Range into LOS1mA to +9mA                               |

| Differential Input Voltage (IN+ - IN-)2.5V                      |

| Continuous Current Range at CML Outputs                         |

| (OUT+, OUT-)25mA to +25mA                                       |

Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

| TQFN (derate 17.7mW above +70°C)                              | 1.4W     |

|---------------------------------------------------------------|----------|

| Operating Junction Temperature Range (T <sub>J</sub> )55°C to | ) +150°C |

| Storage Ambient Temperature Range (T <sub>S</sub> )55°C to    | ) +150°C |

| Lead Temperature (soldering, 10s)                             | +260°C   |

| Soldering Temperature (reflow)                                |          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 2.97V \text{ to } 3.63V, \text{ ambient temperature} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ CML output load is } 50\Omega \text{ to } V_{CC}, \text{ } C_{AZ} = 0.1\mu\text{F}, \text{ typical values are at } T_A = +25^{\circ}\text{C}, V_{CC} = 3.3V, \text{ unless otherwise specified. The data input transition time is controlled by a 4th-order Bessel filter with } f_{-3dB} = 0.75 \times 2.667\text{GHz}$  for all data rates of 2.667Gbps and below, and with  $f_{-3dB} = 0.75 \times \text{data rate for data rates} > 3.2\text{Gbps.})$

| PARAMETER                                   | SYMBOL              | CONDITIONS                                                                    | MIN  | TYP | MAX  | UNITS             |  |

|---------------------------------------------|---------------------|-------------------------------------------------------------------------------|------|-----|------|-------------------|--|

| Single-Ended Input Resistance               |                     | Single-ended to V <sub>CC</sub> (Note 1)                                      | 42   | 50  | 58   | Ω                 |  |

| Input Return Loss                           |                     | Differential, f < 3GHz, DUT is powered on                                     |      | 13  |      | dB                |  |

| Input Sensitivity                           | V <sub>IN-MIN</sub> | (Note 2)                                                                      |      |     | 5    | mV <sub>P-P</sub> |  |

| Input Overload                              | V <sub>IN-MAX</sub> | (Note 2)                                                                      | 1200 |     |      | mV <sub>P-P</sub> |  |

| Single-Ended Output Resistance              |                     | Single-ended to V <sub>CC</sub> (Note 1)                                      | 42   | 50  | 58   | Ω                 |  |

| Output Return Loss                          |                     | Differential, f < 3GHz, DUT is powered on                                     |      | 10  |      | dB                |  |

| Differential Output Voltage                 |                     |                                                                               | 600  | 780 | 1200 | mV <sub>P-P</sub> |  |

| Differential Output Signal when<br>Disabled |                     | Outputs AC-coupled, V <sub>IN-MAX</sub> applied to input (Note 1)             |      |     | 10   | mV <sub>P-P</sub> |  |

| Deterministic Jitter<br>(Notes 1, 3)        |                     | K28.5 pattern at 4.25Gbps                                                     |      | 8.7 | 25   | psp_p             |  |

|                                             | DJ                  | K28.5 pattern at 3.2Gbps                                                      |      | 8.5 | 25   |                   |  |

|                                             |                     | 2 <sup>23</sup> - 1 PRBS equivalent pattern at 2.7Gbps (Note 4)               |      | 9.3 | 30   |                   |  |

|                                             |                     | K28.5 pattern at 2.1Gbps                                                      |      | 7.8 | 25   |                   |  |

|                                             |                     | 2 <sup>23</sup> - 1 PRBS equivalent pattern at 155Mbps                        |      | 25  | 55   |                   |  |

| Random Jitter                               |                     | $Input = 5mV_{P-P}$                                                           |      | 6.5 |      |                   |  |

| (Note 5)                                    |                     | $Input = 10mV_{P-P}$                                                          |      | 3   |      | ps <sub>RMS</sub> |  |

| Data Output Transition Time                 |                     | 20% to 80%, 4.25Gbps, 3.1875GHz Bessel input filter, $V_{IN}$ = 20m $V_{P-P}$ |      | 60  |      | ps                |  |

|                                             |                     | 20% to 80% (Note 1)                                                           |      | 86  | 115  |                   |  |

| Input-Referred Noise                        |                     |                                                                               |      | 185 |      | μV <sub>RMS</sub> |  |

| Low-Frequency Cutoff                        |                     | C <sub>AZ</sub> = open                                                        |      | 70  |      | 1.1.1-            |  |

|                                             |                     | $C_{AZ} = 0.1 \mu F$                                                          |      | 0.8 |      | kHz               |  |

| Device Oversely Overset                     |                     | (Note 6)                                                                      |      | 32  | 49   | — mA              |  |

| Power-Supply Current                        | ICC                 | LOS disabled                                                                  |      |     | 37   |                   |  |

| Power-Supply Noise Rejection                | PSNR                | f < 2MHz                                                                      |      | 26  |      | dB                |  |

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

### ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = 2.97V \text{ to } 3.63V, \text{ ambient temperature} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{CML output load is } 50\Omega \text{ to } V_{CC}, \text{ } C_{AZ} = 0.1\mu\text{F}, \text{ typical values are at } T_A = +25^{\circ}\text{C}, V_{CC} = 3.3V, \text{ unless otherwise specified. The data input transition time is controlled by a 4th-order Bessel filter with } f_{-3dB} = 0.75 \times 2.667\text{GHz}$  for all data rates of 2.667Gbps and below, and with  $f_{-3dB} = 0.75 \times \text{data rate for data rates} > 3.2\text{Gbps.})$

| PARAMETER                   | SYMBOL            | CONDITIONS                                                                      |                           | MIN  | ТҮР  | MAX  | UNITS             |

|-----------------------------|-------------------|---------------------------------------------------------------------------------|---------------------------|------|------|------|-------------------|

| LOSS OF SIGNAL AT 4.25Gbps  | K28.5 PATTI       | ERN (Note 1)                                                                    |                           |      |      |      |                   |

| LOS Hysteresis              |                   | 10log (V <sub>DEASSERT</sub> /V <sub>ASSER</sub>                                | T)                        | 1.25 | 2.2  |      | dB                |

| LOS Assert/Deassert Time    |                   | (Note 7)                                                                        |                           | 2    |      | 100  | μs                |

| LOS Assert                  |                   | $R_{TH} = 280 k\Omega$                                                          |                           |      | 18.5 |      | mV <sub>P-P</sub> |

| LOS Deassert                |                   | $R_{TH} = 280 k\Omega$                                                          |                           |      | 28   |      | mV <sub>P-P</sub> |

| LOSS OF SIGNAL AT 2.5Gbps   | Notes 2, 8)       |                                                                                 |                           |      |      |      |                   |

| LOS Hysteresis              |                   | 10log (V <sub>DEASSERT</sub> /V <sub>ASSER</sub>                                | T)                        | 1.25 | 2.2  |      | dB                |

| LOS Assert/Deassert Time    |                   | (Note 7)                                                                        |                           | 2    |      | 100  | μs                |

| Low LOS Assert Level        |                   | $R_{TH} = 20k\Omega$                                                            |                           |      | 4.8  |      | mV <sub>P-P</sub> |

| Low LOS Deassert Level      |                   | $R_{TH} = 20k\Omega$                                                            |                           |      | 7.7  | 13.6 | mV <sub>P-P</sub> |

| Medium LOS Assert Level     |                   | $R_{TH} = 280\Omega$                                                            |                           | 10.3 | 15.2 |      | mV <sub>P-P</sub> |

| Medium LOS Deassert Level   |                   | R <sub>TH</sub> = 280Ω                                                          |                           |      | 25   | 38.6 | mV <sub>P-P</sub> |

| High LOS Assert Level       |                   | $R_{TH} = 80\Omega$                                                             |                           | 22.8 | 38.3 |      | mV <sub>P-P</sub> |

| High LOS Deassert Level     |                   | $R_{TH} = 80\Omega$                                                             |                           |      | 65.2 | 99.3 | mV <sub>P-P</sub> |

| LOSS OF SIGNAL AT 155Mbps   | (Note 8)          |                                                                                 |                           |      |      |      |                   |

| LOS Hysteresis              |                   | 10log (V <sub>DEASSERT</sub> /V <sub>ASSER</sub>                                | T)                        |      | 2.1  |      | dB                |

| LOS Assert/Deassert Time    |                   | (Note 7)                                                                        |                           |      | 20   |      | μs                |

| Low LOS Assert Level        |                   | $R_{TH} = 20k\Omega$                                                            |                           |      | 3.5  |      | mV <sub>P-P</sub> |

| Low LOS Deassert Level      |                   | $R_{TH} = 20k\Omega$                                                            |                           |      | 5.6  |      | mV <sub>P-P</sub> |

| Medium LOS Assert Level     |                   | $R_{TH} = 280\Omega$                                                            |                           |      | 13.3 |      | mV <sub>P-P</sub> |

| Medium LOS Deassert Level   |                   | R <sub>TH</sub> = 280Ω                                                          |                           |      | 21.2 |      | mV <sub>P-P</sub> |

| High LOS Assert Level       |                   | $R_{TH} = 80\Omega$                                                             |                           |      | 33.3 |      | mV <sub>P-P</sub> |

| High LOS Deassert Level     |                   | $R_{TH} = 80\Omega$                                                             |                           |      | 55.5 |      | mV <sub>P-P</sub> |

| RSSI                        |                   |                                                                                 |                           |      |      |      |                   |

| RSSI Current Gain           | A <sub>RSSI</sub> | A <sub>RSSI</sub> = I <sub>RSSI</sub> /I <sub>CM_RSSI</sub> (N                  | ote 9)                    |      | 0.03 |      |                   |

| Input-Referred RSSI Current |                   | I <sub>RSSI</sub> /A <sub>RSSI</sub>                                            | р <sub>UT</sub> < 6.6mA   | -57  |      | +57  |                   |

| Stability                   |                   | (Note 10)                                                                       | <sub>PUT</sub> > 6.6mA    | -118 |      | +112 | μA                |

| TTL/CMOS I/O                |                   |                                                                                 |                           |      |      |      |                   |

| LOS Output High Voltage     | V <sub>OH</sub>   | $R_{LOS}$ = 4.7k $\Omega$ to10k $\Omega$ to V                                   | / <sub>CC_HOST</sub> (3V) | 2.4  |      |      | V                 |

| LOS Output Low Voltage      | V <sub>OL</sub>   | $R_{LOS} = 4.7 k\Omega$ to 10k $\Omega$ to V <sub>CC_HOST</sub> (3.6V)          |                           |      |      | 0.4  | V                 |

| LOS Output Current          |                   | $R_{LOS} = 4.7$ kΩ to10kΩ to V <sub>CC_HOST</sub> (3.3V);<br>IC is powered down |                           |      |      | 40   | μA                |

| DISABLE Input High          | VIH               |                                                                                 |                           | 2.0  |      |      | V                 |

| DISABLE Input Low           | V <sub>IL</sub>   |                                                                                 |                           |      |      | 0.8  | V                 |

| DISABLE Input Current       |                   | $R_{LOS} = 4.7 k\Omega$ to $10 k\Omega$ to $10 k\Omega$                         | V <sub>CC HOST</sub>      |      |      | 10   | μA                |

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

### ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = 2.97V \text{ to } 3.63V, \text{ ambient temperature} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ CML output load is } 50\Omega \text{ to } V_{CC}, C_{AZ} = 0.1\mu\text{F}, \text{ typical values are}$  at  $T_A = +25^{\circ}\text{C}$ ,  $V_{CC} = 3.3V$ , unless otherwise specified. The data input transition time is controlled by a 4th-order Bessel filter with  $f_{-3dB} = 0.75 \times 2.667\text{GHz}$  for all data rates of 2.667Gbps and below, and with  $f_{-3dB} = 0.75 \times \text{data rate}$  for data rates > 3.2Gbps.)

- Note 1: Guaranteed by design and characterization.

- Note 2: Between sensitivity and overload, all AC specifications are met.

- Note 3: The deterministic jitter caused by this filter is not included in the DJ generation specifications (input).

- **Note 4:** 2<sup>23</sup> 1 PRBS pattern was substituted by K28.5 pattern to determine the high-speed portion of the deterministic jitter. The low-speed portion of the DJ (baseline wander) was obtained by measuring the eye width difference between outputs generated using K28.5 and 2<sup>23</sup> 1 PRBS patterns.

- Note 5: Random jitter was measured without using a filter at the input.

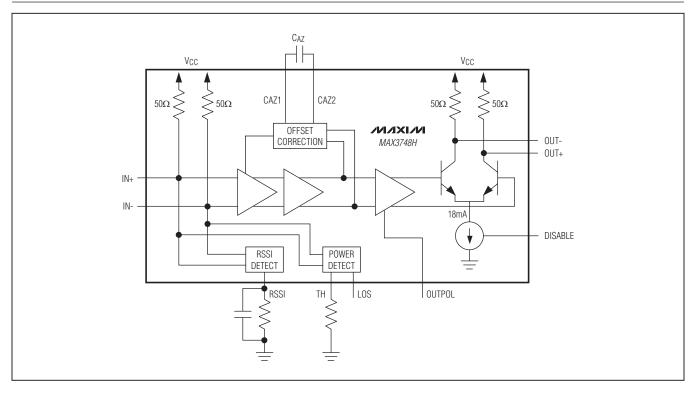

- Note 6: The supply current measurement excludes the CML output currents by connecting the CML outputs to a separate V<sub>CC</sub> (see Figure 1).

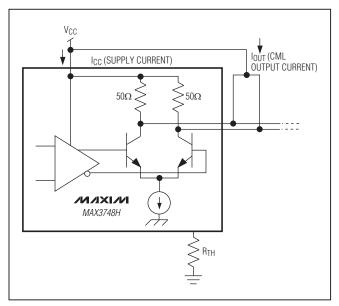

- Note 7: The signal at the input is switched between two amplitudes, Signal\_ON and Signal\_OFF, as shown in Figure 2.

- **Note 8:** Unless otherwise specified, the pattern for all LOS detect specifications is 2<sup>23</sup> 1 PRBS.

- Note 9: I<sub>CM INPUT</sub> is the input common mode. I<sub>RSSI</sub> is the current at the RSSI output.

- Note 10: Stability is defined as variation over temperature and power supply with respect to the typical gain of the part.

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

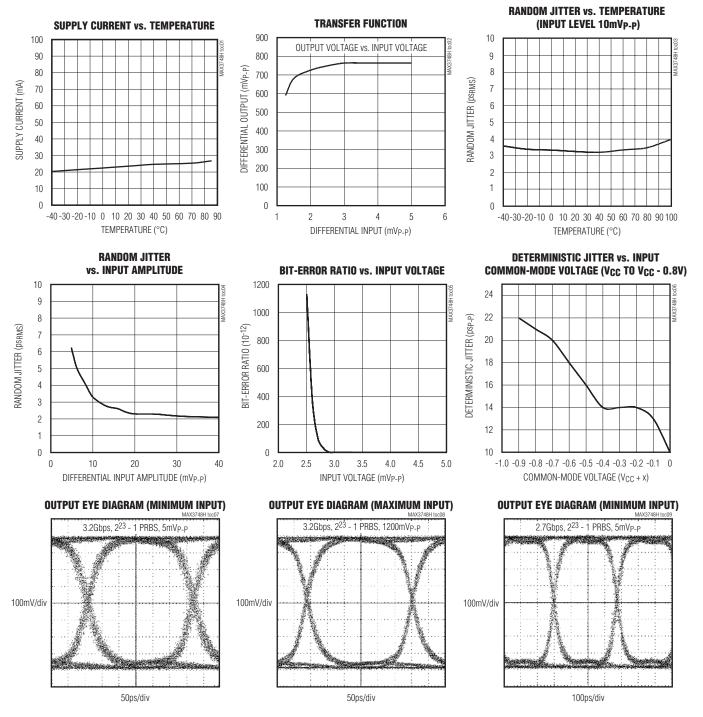

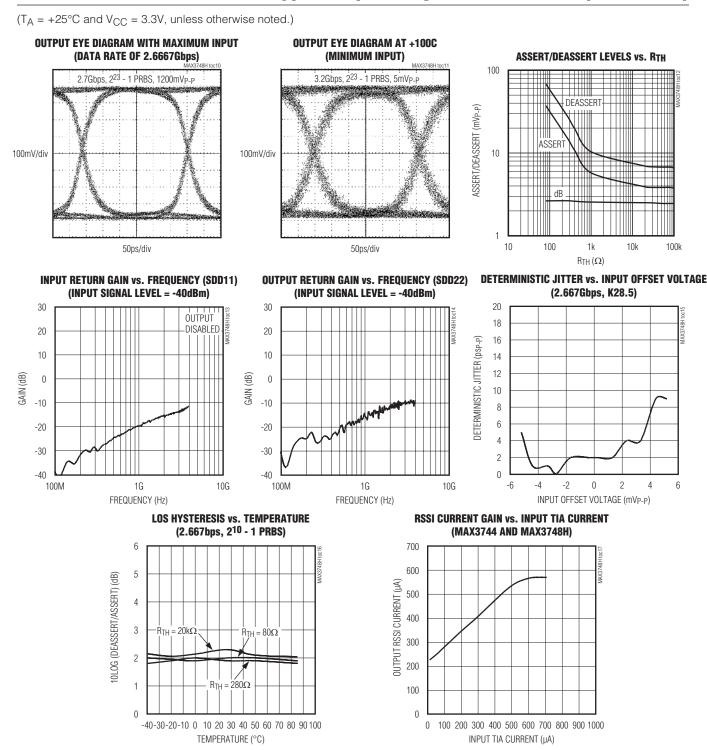

(T<sub>A</sub> = +25°C and V<sub>CC</sub> = 3.3V, unless otherwise noted.)

### **Typical Operating Characteristics**

# MAX3748H Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

**Typical Operating Characteristics (continued)**

Maxim Integrated Products 6

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

## **Pin Configuration**

## **Pin Description**

| PIN      | NAME            | FUNCTION                                                                                                                                                                                                                                                                      |

|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 12 | V <sub>CC</sub> | Supply Voltage                                                                                                                                                                                                                                                                |

| 2        | IN+             | Noninverted Input Signal, CML                                                                                                                                                                                                                                                 |

| 3        | IN-             | Inverted Input Signal, CML                                                                                                                                                                                                                                                    |

| 5        | TH              | Loss-of-Signal Threshold Pin. Resistor to ground ( $R_{TH}$ ) sets the LOS threshold. Connecting this pin to $V_{CC}$ disables the LOS circuitry and reduces power consumption.                                                                                               |

| 6        | DISABLE         | Disable Input, CMOS/TTL. The data outputs are held static when this pin is asserted high. The LOS function remains active when the outputs are disabled. If routed through the DS1858/DS1859 controller IC, no additional ESD protection is required.                         |

| 7        | LOS             | Noninverted Loss-of-Signal Output. LOS is asserted high when the signal drops below the assert threshold set by the TH input. The output is open collector (Figure 5). If routed through the DS1858/DS1859 controller IC, no additional ESD protection is required.           |

| 8, 16    | GND             | Supply Ground                                                                                                                                                                                                                                                                 |

| 9        | OUTPOL          | Output Polarity Control Input. Connect to GND for an inversion of polarity through the limiting amplifier and connect to $V_{CC}$ for normal operation.                                                                                                                       |

| 10       | OUT-            | Inverted Data Output, CML                                                                                                                                                                                                                                                     |

| 11       | OUT+            | Noninverted Data Output, CML                                                                                                                                                                                                                                                  |

| 13       | RSSI            | Received-Signal-Strength Indicator. This current output can be used to obtain a ground-referenced voltage proportional to photodiode current with the MAX3744 by connecting an external resistor between this pin and GND.                                                    |

| 14       | CAZ2            | Offset Correction Loop Capacitor Connection. A capacitor connected between this pin and CAZ1 extends the time constant of the offset correction loop. Typical value of $C_{AZ}$ is 0.1µF. The offset correction is disabled when the CAZ1 and CAZ2 pins are shorted together. |

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

## **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                      |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | CAZ1 | Offset Correction Loop Capacitor Connection. A capacitor connected between this pin and CAZ2 extends the time constant of the offset correction loop. Typical value of $C_{AZ}$ is 0.1µF. The offset correction is disabled when the CAZ1 and CAZ2 pins are shorted together. |

| _   | EP   | Exposed Pad. Connect the exposed pad to board ground for optimal electrical and thermal performance.                                                                                                                                                                          |

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

### **Detailed Description**

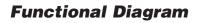

The MAX3748H limiting amplifier consists of an input buffer, a multistage amplifier, offset correction circuitry, an output buffer, power-detection circuitry, and signaldetect circuitry (see the *Functional Diagram*).

Figure 1. Power-Supply Current Measurement

Figure 2. LOS Deassert Threshold Set 1dB Below the Minimum by Receiver Sensitivity (for Selected  $R_{TH}$ )

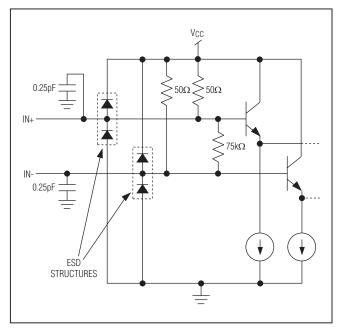

#### **Input Buffer**

The input buffer is shown in Figure 3. It provides  $50\Omega$  termination for each input signal IN+ and IN-. The MAX3748H can be DC- or AC-coupled to a TIA (TIA output offset degrades receiver performance if DC-coupled). The MAX3748H CML input buffer is optimized for the MAX3744 TIA.

#### **Gain Stage**

The high-bandwidth gain stage provides approximately 53dB of gain.

#### **Offset Correction Loop**

The MAX3748H is susceptible to DC offsets in the signal path because they have high gain. In communication systems using NRZ data with a 50% duty cycle, pulsewidth distortion present in the signal or generated in the transimpedance amplifier appears as an input offset and is reduced by the offset correction loop. For Gigabit Ethernet and Fibre Channel applications, no capacitor is required. For SONET applications,  $C_{AZ} = 0.1 \mu F$  is recommended. This capacitor determines the lower 3dB frequency of the data path.

Figure 3. CML Input Buffer

## Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

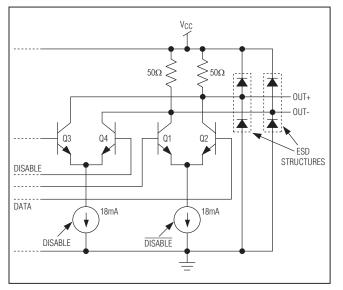

#### **CML Output Buffer**

The MAX3748H limiting amplifier's CML output provides high tolerance to impedance mismatches and inductive connectors. The output current is approximately 18mA. The output is disabled by connecting the DISABLE pin to V<sub>CC</sub>. If the LOS pin is connected to the DISABLE pin, the outputs OUT+ and OUT- are at a static voltage (squelch) whenever the input signal level drops below the LOS threshold. The output buffer can be AC- or DC-coupled to the load (Figure 4).

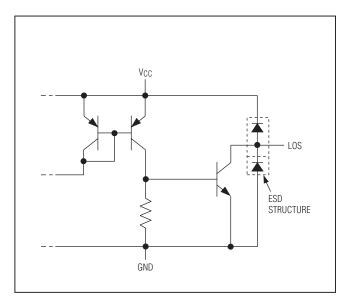

**Power-Detect and Loss-of-Signal Indicator** The MAX3748H is equipped with LOS circuitry, which indicates when the input signal is below a programmable threshold, set by resistor R<sub>TH</sub> at the TH pin (see the *Typical Operating Characteristics* for appropriate resistor sizing). An averaging peak-power detector compares the input signal amplitude with this threshold and feeds the signal detect information to the LOS output, which is open collector. Two control voltages, V<sub>ASSERT</sub> and V<sub>DEASSERT</sub>, define the LOS assert and deassert levels. To prevent LOS chatter in the region of the programmed threshold, approximately 2dB of hysteresis is built into the LOS assert/deassert function. Once asserted, LOS

Figure 4. CML Output Buffer

is not deasserted until the input amplitude rises to the required level ( $V_{DEASSERT}$ ) (Figure 5).

### **Design Procedure**

#### **Program the LOS Assert Threshold**

External resistor R<sub>TH</sub> programs the LOS threshold. See the Assert/Deassert Levels vs. R<sub>TH</sub> graph in the *Typical Operating Characteristics* to select the appropriate resistor.

#### Select the Coupling Capacitor

When AC-coupling is desired, coupling capacitors  $C_{IN}$  and  $C_{OUT}$  should be selected to minimize the receiver's deterministic jitter. Jitter is decreased as the input low-frequency cutoff ( $f_{IN}$ ) is decreased:

#### $f_{IN} = 1/[2\pi(50)(C_{IN})]$

For ATM/SONET or other applications using scrambled NRZ data, select (C<sub>IN</sub>, C<sub>OUT</sub>)  $\geq$  0.1µF, which provides f<sub>IN</sub> < 32kHz. For Fibre Channel, Gigabit Ethernet, or other applications using 8B/10B data coding, select (C<sub>IN</sub>, C<sub>OUT</sub>)  $\geq$  0.01µF, which provides f<sub>IN</sub> < 320kHz. Refer to Application Note 292: *HFAN-1.1: Choosing AC-Coupling Capacitors*.

Figure 5. MAX3748H LOS Output Circuit

## Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

#### Select the Offset-Correction Capacitor

The capacitor between CAZ1 and CAZ2 determines the time constant of the signal path DC offset cancellation loop. To maintain stability, it is important to keep a onedecade separation between  $f_{IN}$  and the low-frequency cutoff ( $f_{OC}$ ) associated with the DC offset cancellation circuit. For ATM/SONET or other applications using scrambled NRZ data,  $f_{IN} < 32$ kHz, so  $f_{OCMAX} < 3.2$ kHz. Therefore,  $C_{AZ} = 0.1 \mu$ F ( $f_{OC} = 2$ kHz). For Fibre Channel or Gigabit Ethernet applications, leave pins CAZ1 and CAZ2 open.

#### **RSSI** Implementation

The SFF-8472 Digital Diagnostic specification requires monitoring of input receive power. The MAX3748H and MAX3744 receiver chipset allows for the monitoring of the average receive power by measuring the average DC current of the photodiode.

The MAX3744 preamp measures the average photodiode current and provides the information to the output common mode. The MAX3748H RSSI detect block senses the common-mode DC level of input signals IN+ and IN- and provides a ground-referenced output signal (RSSI) proportional to the photodiode current. The advantage of this implementation is that it allows the TIA to be packaged in a low-cost conventional 4-pin TO-46 header. The MAX3748H RSSI output is connected to an analog input channel of the DS1858/DS1859 SFP controller to convert the analog information into a 16-bit word. The DS1858/DS1859 provide the receive-power information to the host board of the optical receiver through a 2-wire interface. The DS1859 allows for internal calibration of the receive-power monitor.

The MAX3744 and the MAX3748H have been optimized to achieve RSSI stability of 2.5dB within the  $6\mu$ A to 500 $\mu$ A range of average input photodiode current. To achieve the best accuracy, Maxim recommends receive power calibration at the low end ( $6\mu$ A) and the high end ( $500\mu$ A) of the required range; see the RSSI Current Gain vs. Input TIA Current graph in the <u>Typical Operating</u> Characteristics.

#### Connecting to the DS1858/DS1859

For best use of the RSSI monitor, capacitor C1 and resistor R1 shown in the *Typical Operating Circuits* (see first graphic) need to be placed as close as possible to the Maxim diagnostic monitor with the ground of C1 and R1 the same as the DS1858/DS1859 ground. Capacitor C1 suppresses system noise on the RSSI signal. R1 =  $3k\Omega$  and C1 =  $0.1\mu$ F is recommended.

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

**Typical Operating Circuits (continued)**

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

### **Chip Information**

PROCESS: SiGe BIPOLAR

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX3748HETE+ | -40°C to +85°C | 16 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maxim-ic.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE        | LAND           |

|------------|---------|----------------|----------------|

| TYPE       | CODE    | NO.            | PATTERN NO.    |

| 16 TQFN-EP | T1633+5 | <u>21-0136</u> | <u>90-0031</u> |

# Compact, Low-Power, 155Mbps to 4.25Gbps Limiting Amplifier

## **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 7/11     | Initial release | —       |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

Maxim is a registered trademark of Maxim Integrated Products, Inc.

\_ 14