#### INSULATED GATE BIPOLAR TRANSISTOR

#### **Features**

- Low V<sub>CE (ON)</sub> Trench IGBT Technology

- Low Switching Losses

- Maximum Junction Temperature 175 °C

- Short Circuit Rated

- Square RBSOA

- Positive V<sub>CE (ON)</sub> Temperature Coefficient

- Tight Parameter Distribution

- Integrated Gate Resistor

| G    | С         | Е       |  |

|------|-----------|---------|--|

| Gate | Collector | Emitter |  |

#### **Benefits**

- High Efficiency in a Wide Range of Applications

- Suitable for a Wide Range of Switching Frequencies due to Low  $V_{CE\,(ON)}$  and Low Switching Losses

- Rugged Transient Performance for Increased Reliability

- Excellent Current Sharing in Parallel Operation

- Easier Paralleling with Integrated Gate Resistor

## **Applications**

- **Industrial Motor Drives**

- Inverter

- **UPS**

- Welding

| Page part number | Bookaga Typa | Standa      | rd Pack | Oudevelle west susselves |  |

|------------------|--------------|-------------|---------|--------------------------|--|

| Base part number | Package Type | Form Quanti |         | Orderable part number    |  |

| IRGC4275B        | Die on Film  | Wafer       | 1       | IRGC4275B                |  |

#### **Mechanical Parameters**

| Die Size                            | 10 x 10 mm                                 |                 |  |

|-------------------------------------|--------------------------------------------|-----------------|--|

| Minimum Street Width                | 75                                         | μm              |  |

| Emiter Pad Size (Included Gate Pad) | See Die Drawing                            |                 |  |

| Gate Pad Size                       | 1.0 x 1.717                                | mm <sup>2</sup> |  |

| Area Total / Active                 | 100/ 81.89                                 |                 |  |

| Thickness                           | 70                                         | μm              |  |

| Wafer Size                          | 150                                        | mm              |  |

| Flat Position                       | 0                                          | Degrees         |  |

| Maximum-Possible Chips per Wafer    | 136pcs.                                    |                 |  |

| Passivation Front side              | Silicon Nitride                            |                 |  |

| Front Metal                         | Al, Si (4μm)                               |                 |  |

| Backside Metal                      | AI (1kA°), Ti (1kA°), Ni (4kA°), Ag (6kA°) |                 |  |

| Die Bond                            | Electrically conductive epoxy or solder    |                 |  |

| Reject Ink Dot Size                 | 0.25 mm diameter minimum black             |                 |  |

**Maximum Ratings**

|                                   | Parameter                                       | Max.        | Units |

|-----------------------------------|-------------------------------------------------|-------------|-------|

| $V_{CE}$                          | Collector-Emitter Voltage, T <sub>J</sub> =25°C | 650         | V     |

| $I_{C}$                           | DC Collector Current                            | •           | Α     |

| I <sub>LM</sub>                   | Clamped Inductive Load Current 4                | 800         | Α     |

| $V_{\sf GE}$                      | Gate Emitter Voltage                            | ± 20        | V     |

| T <sub>J</sub> , T <sub>STG</sub> | Operating Junction and Storage Temperature      | -40 to +175 | °C    |

# Static Characteristics (Tested on wafers) . T<sub>J</sub>=25°C

|                         | Parameter                              | Min. | Тур. | Max.  | Units | Conditions                                        |

|-------------------------|----------------------------------------|------|------|-------|-------|---------------------------------------------------|

| V <sub>(BR)CES</sub>    | Collector-to-Emitter Breakdown Voltage | 650  |      |       |       | V <sub>GE</sub> = 0V, I <sub>C</sub> = 100μA ⑤    |

| V <sub>CE(sat)</sub>    | Collector-to-Emitter Saturated Voltage |      | 1.6  | 1.9   | V     | $V_{GE} = 15V, I_{C} = 200A, T_{J} = 25^{\circ}C$ |

| $V_{GE(th)}$            | Gate-Emitter Threshold Voltage         | 5.5  |      | 7.7   |       | $I_C = 6.6$ mA, $V_{GE} = V_{CE}$                 |

| I <sub>CES</sub>        | Zero Gate Voltage Collector Current    |      | 1.0  | 20    | μΑ    | $V_{CE} = 650V, V_{GE} = 0V$                      |

| I <sub>GES</sub>        | Gate Emitter Leakage Current           |      |      | ± 600 | nA    | $V_{CE} = 0V$ , $V_{GE} = \pm 20V$                |

| R <sub>G INTERNAL</sub> | Internal Gate Resistance               | 1.6  | 2.0  | 2.4   | Ω     |                                                   |

# Electrical Characteristics (Not subject to production test- Verified by design/characterization)

|                      | Parameter                              | Min.        | Тур.  | Max. | Units                                                                                                         | Conditions                                                                              |

|----------------------|----------------------------------------|-------------|-------|------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| V <sub>CE(sat)</sub> | Collector-to-Emitter Saturated Voltage |             | 1.6   | 1.9  |                                                                                                               | V <sub>GE</sub> = 15V, I <sub>C</sub> = 200A , T <sub>J</sub> = 25°C                    |

| 02(001)              |                                        |             | 2.0   |      |                                                                                                               | V <sub>GE</sub> = 15V, I <sub>C</sub> = 200A , T <sub>J</sub> = 175°C                   |

| SCSOA                | Short Circuit Safe Operating Area      | 5.5         |       |      |                                                                                                               | $V_{GE} = 15V, V_{CC} = 400V, ②$<br>$R_G = 5.0\Omega, V_P \le 600V, T_J = 150^{\circ}C$ |

| RBSOA                | Reverse Bias Safe Operating Area       | FULL SQUARE |       |      | $T_J$ = 175°C, $I_C$ = 800A<br>$V_{CC}$ = 480V, $V_D \le 600V$<br>$Rg$ = 5.0 $\Omega$ , $V_{GE}$ = +20V to 0V |                                                                                         |

| C <sub>iss</sub>     | Input Capacitance                      |             | 12940 |      |                                                                                                               | V <sub>GE</sub> = 0V                                                                    |

| Coss                 | Output Capacitance                     |             | 650   |      | pF                                                                                                            | V <sub>CE</sub> = 30V                                                                   |

| $C_{rss}$            | Reverse Transfer Capacitance           |             | 340   |      |                                                                                                               | f = 1.0MHz                                                                              |

| $Q_g$                | Total Gate Charge (turn-on)            | _           | 380   | _    |                                                                                                               | I <sub>C</sub> = 200A ⑥                                                                 |

| $Q_{ge}$             | Gate-to-Emitter Charge (turn-on)       | _           | 140   | _    | nC                                                                                                            | V <sub>GE</sub> = 15V                                                                   |

| $Q_{gc}$             | Gate-to-Collector Charge (turn-on)     | _           | 170   | _    |                                                                                                               | V <sub>CC</sub> = 400V                                                                  |

# Switching Characteristics (Inductive Load-Not subject to production test-Verified by design/characterization)

|                    | Parameter           | Min. | Тур. | Max. | Units | Conditions ③                                  |

|--------------------|---------------------|------|------|------|-------|-----------------------------------------------|

| t <sub>d(on)</sub> | Turn-On delay time  | _    | 130  |      |       | I <sub>C</sub> = 200A, V <sub>CC</sub> = 400V |

| $t_r$              | Rise time           |      | 330  | _    |       | $R_G = 5.0\Omega$ , $V_{GE} = 15V$            |

| $t_{d(off)}$       | Turn-Off delay time | _    | 280  | _    |       | T <sub>J</sub> = 25°C                         |

| $t_f$              | Fall time           | _    | 140  |      |       |                                               |

| $t_{d(on)}$        | Turn-On delay time  | _    | 115  |      | ns    | $I_C = 200A$ , $V_{CC} = 400V$                |

| t <sub>r</sub>     | Rise time           |      | 330  | _    |       | $R_G = 5.0\Omega, V_{GE} = 15V$               |

| $t_{d(off)}$       | Turn-Off delay time | _    | 330  | _    |       | T <sub>J</sub> = 175°C                        |

| t <sub>f</sub>     | Fall time           | _    | 160  |      | 1     |                                               |

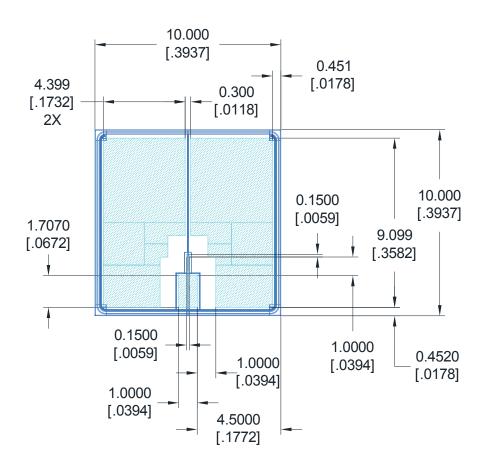

# Die Drawing

## NOTES:

- 1. ALL DIMENSIONS ARE SHOWN IN MILLIMETERS [INCHES].

- 2. CONTROLLING DIMENSION: INCHES

- 3. DIE WIDTH AND LENGTH TOLERANCE: -0.0508 [.002]

- 4. DIE THICKNESS = 0.070 [.00276]

REFERENCE: IRGC4275B IRGC4275F

#### Notes:

- $\odot$  The current in the application is limited by  $T_{JMax}$  and the thermal properties of the assembly.

- ② Not subject to production test- Verified by design / characterization.

- ③ Values influenced by parasitic L and C in measurement.

- Φ V<sub>CC</sub> = 80% (V<sub>CES</sub>), V<sub>GE</sub> = 20V, L = 66μH, R<sub>G</sub> = 5.0Ω.

- S Refer to AN-1086 for guidelines for measuring V<sub>(BR)CES</sub> safely

- © Die Level Characterization.

#### **Additional Testing and Screening**

For Customers requiring product supplied as Known Good Die (KGD) or requiring specific die level testing, please contact your local IR Sales

#### **Shipping**

Sawn Wafer on Film. Please contact your local IR sales office for non-standard shipping options

### Handling

- Product must be handled only at ESD safe workstations. Standard ESD precautions and safe work environments are as defined in MIL-HDBK-263.

- Product must be handled only in a class 10,000 or better-designated clean room environment.

- Singulated die are not to be handled with tweezers. A vacuum wand with a non-metallic ESD protected tip should be used.

# Wafer/Die Storage

- Proper storage conditions are necessary to prevent product contamination and/or degradation after shipment.

- Note: To reduce the risk of contamination or degradation, it is recommended that product not being used in the

assembly process be returned to their original containers and resealed with a vacuum seal process.

- Sawn wafers on a film frame are intended for immediate use and have a limited shelf life.

#### **Further Information**

For further information please contact your local IR Sales office. http://die.irf.com

#### **Revision History**

| Date       | Comments                                                                                  |  |  |  |

|------------|-------------------------------------------------------------------------------------------|--|--|--|

|            | Updated IFX logo on all pages                                                             |  |  |  |

| 07/02/2015 | <ul> <li>Removed Vcesat @ I<sub>C</sub> = 20A, V<sub>GE</sub> = 15V on page 2.</li> </ul> |  |  |  |

|            | <ul> <li>Added Vcesat @ I<sub>C</sub> = 200A, V<sub>GE</sub> = 15V on page 2.</li> </ul>  |  |  |  |

IR WORLD HEADQUARTERS: 101 N. Sepulveda Blvd., El Segundo, California 90245, USA To contact International Rectifier, please visit <a href="http://www.irf.com/whoto-call/">http://www.irf.com/whoto-call/</a>